# AN1124

# 1M to 4M DRAM Upgrading

# Prepared by: Paul Oats

4M DRAM Product Engineering Austin, Texas

# INTRODUCTION

Standards set through JEDEC and EIAJ allow upward compatibility from the 1M to 4M DRAM by using the same pinout for SOJ and ZIP packages. Such standards are set to ensure a stable DRAM supply when higher density memories are introduced. This eliminates the need for expensive redesigns of systems that can utilize the new memories.

Although the common pinout between the 1M and 4M DRAM requires little, if any, relayout of the PCB, caution must be exercised when upgrading because of potential incompatibilities with refresh and power up. Both of these involve differences in test mode entry between the 1M and 4M DRAM.

### REFRESH

The dynamic memory cell is based on capacitor charge storage for each bit in the array. This charge will dissipate over time, so the entire array must periodically be refreshed to maintain the correct bit state. This is accomplished by cycling through all the rows of the array within a specified refresh time.

The 4M DRAM has 1024 rows instead of the 1M's 512 rows. Since the refresh period of the 4M is twice that of the 1M DRAM, the equivalent wait state of the 4M is the same as that of the 1M. This is summarized in Table 1.

Like the 1M DRAM, the 4M DRAM can be refreshed through a variety of ways: any read or write cycle, a  $\overline{RAS}$ only refresh, a  $\overline{CAS}$  before  $\overline{RAS}$  refresh, or a hidden refresh. A potential incompatibility between the 1M and 4M DRAM exists with the use of the  $\overline{CAS}$  before  $\overline{RAS}$  refresh.

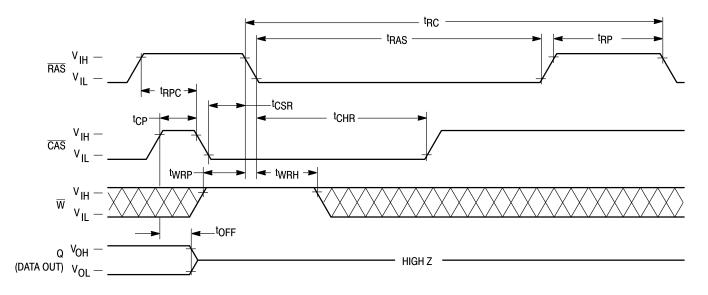

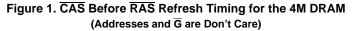

On the 1M DRAM, the  $\overline{W}$  pin is specified as a don't care during the  $\overline{CAS}$  before  $\overline{RAS}$  refresh. But on the 4M DRAM, the  $\overline{W}$  pin must be high (disabled) for time t<sub>WRP</sub> before  $\overline{RAS}$ goes low and held high for time t<sub>WRH</sub> after the transition. This will prevent the device from entering the JEDEC standard test mode. Figure 1 shows the CAS before RAS refresh timing for the 4M DRAM, and Figure 2 shows the test mode entry timing. The test mode is exited by performing either a RAS-only refresh cycle or a CAS before RAS refresh cycle. Test mode on the 1M DRAM is entered through use of a "supervoltage" on a separate test function pin, and is therefore completely unlike the 4M test mode entry.

# **POWER UP**

Another potential incompatibility between the 1M and 4M DRAM occurs during the power up, and this must be addressed when upgrading. Both devices require a pause of 200  $\mu$ s after power up, followed by 8 RAS cycles before proper device operation is guaranteed. The pause allows the internal substrate generator to establish the correct bias voltage. The 8 RAS cycles initialize all dynamic nodes within the RAM.

To prevent the 4M DRAM from entering the test mode, the 8 RAS cycles should be RAS-only refresh cycles or CAS before RAS refresh cycles. If these refresh modes are not used, the device could power up in the test mode, which can only be exited by performing a RAS-only refresh cycle or a CAS before RAS refresh cycle.

# SUMMARY

Upgrading a system from a 1M DRAM to a 4M DRAM is easily accomplished if a few precautions are taken. The CAS before RAS refresh mode on the 4M DRAM requires that  $\overline{W}$ be high during the RAS low transition. If  $\overline{W}$  is a don't care, as on the 1M DRAM, the test mode could inadvertently be entered. Caution with the 4M DRAM must also be exercised during the power up. The 8 initialization cycles should be either RAS-only refresh cycles or CAS before RAS refresh cycles, so that the device comes up in its normal operating mode and not in the test mode.

| Table 1. Comparison of Refresh Requirements for the 4M and 1M DRAM |

|--------------------------------------------------------------------|

| (Times Shown are for Devices with 70 ns Random Access Times)       |

|                                             | 4M           |           | 1M           |           |

|---------------------------------------------|--------------|-----------|--------------|-----------|

|                                             | Normal Power | Low Power | Normal Power | Low Power |

| Number of Rows                              | 1024         | 1024      | 512          | 512       |

| Number of Bits per Row                      | 4096         | 4096      | 2048         | 2048      |

| Refresh Period (t <sub>RFSH</sub> )         | 16 ms        | 128 ms    | 8 ms         | 64 ms     |

| Distributed Refresh Period                  | 15.6 μs      | 124.8 μs  | 15.6 μs      | 124.8 μs  |

| Burst Refresh Period                        | 16 ms        | 128 ms    | 8 ms         | 64 ms     |

| Time to Refresh 1 Row (t <sub>RC</sub> )    | 130 ns       | 130 ns    | 130 ns       | 130 ns    |

| Cumulative Time to Refresh the Entire Array | 133.1 μs     | 133.1 μs  | 66.6 µs      | 66.6 μs   |

| Refresh Time/Operating Time                 | 0.833%       | 0.104%    | 0.833%       | 0.104%    |

Figure 2. Test Mode Entry Timing for the 4M DRAM

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death Motorola was negligent regarding the design or manufacture of the part. Motorola and use negligent regarding the design or manufacture of the part.

#### Literature Distribution Centers:

USA: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036.

EUROPE: Motorola Ltd.; European Literature Centre; 88 Tanners Drive, Blakelands, Milton Keynes, MK14 5BP, England.

JAPAN: Nippon Motorola Ltd.; 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141, Japan.

0

ASIA PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Center, No. 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong.